文章目录

- 1.variable length encoding (VLE) 可变长度编码

- 2.Error Correction Code(ECC)纠错编码

- 3.Memory protection unit (MPU) 内存保护单元

- 4.Interrupt controller (INTC) 中断控制器

- 5.Frequency modulated phase-locked loop (FMPLL) 频率调制锁相环

- 6.Crossbar switch architecture 交叉开关架构

- 7.Boot assist module (BAM) 引导辅助模块

- 8.Enhanced Modular Input Output System-lite(eMIOS-lite)增强型模块化输入输出系统

- 9.DSPI、SPI、QSPI

- 10.periodic interrupt timers (PIT) 周期性中断定时器

- 11.System Module Timer (STM) 系统模块计时器

- 12.Nexus development interface (NDI) Nexus开发接口

- 13.Joint Test Action Group (JTAG) 联合测试行动组

- 14.On-chip voltage regulator (VREG) 片上电压调节器

- 15.PWM + MC + IC/OC

- 16.四个电流直标

1.variable length encoding (VLE) 可变长度编码

Includes an instruction set enhancement allowing variable length encoding (VLE) for code size footprint

reduction. With the optional encoding of mixed 16-bit and 32-bit instructions, it is possible to achieve significant code size footprint reduction.

包括一种指令集增强,允许可变长度编码(VLE)以减小代码尺寸。通过可选的混合16位和32位指令编码,可以实现显著的代码尺寸减小。

2.Error Correction Code(ECC)纠错编码

3.Memory protection unit (MPU) 内存保护单元

Memory protection unit (MPU) with 8 region descriptors and 32-byte region granularity

该设备具有内存保护单元(MPU),具备8个区域描述符和32字节的区域粒度。

在这里,"区域描述符"指的是用于描述内存保护单元(MPU)中的各个区域的配置参数。每个区域描述符定义了一块内存区域的起始地址、大小以及访问权限等设置。

而"区域粒度"指的是内存保护单元(MPU)中划分内存区域的最小单位大小。在这种情况下,每个区域的大小为32字节,意味着内存可以按照32字节的粒度进行划分。

通过配置区域描述符,可以对内存进行细粒度的保护控制。每个区域的权限设置可以限制对该区域的读取、写入和执行等操作,以提高系统的安全性和稳定性。这种细粒度的内存保护可以在多任务操作系统或多进程环境中确保各个任务或进程之间的内存隔离和保护。

4.Interrupt controller (INTC) 中断控制器

Interrupt controller (INTC) with 148 interrupt vectors, including 16 external interrupt sources and 18 external interrupt/wakeup sources.

具有148个中断向量的中断控制器(INTC),其中包括16个外部中断源和18个外部中断/唤醒源。

5.Frequency modulated phase-locked loop (FMPLL) 频率调制锁相环

频率调制相位锁定环(FMPLL)是一种电路或系统,用于生成稳定的时钟信号。它常用于数字通信系统、调频广播、音频处理等领域。

FMPLL通过将参考频率信号与参考相位进行频率调制,然后与反馈信号进行比较和调整,以维持稳定的输出频率和相位。它通常由相锁环(PLL)和频率调制器(FM)组成。

FMPLL的工作原理是通过频率调制实现相位锁定。它接收一个参考信号作为输入,经过频率调制后得到一个调制信号。然后将这个调制信号与反馈信号进行比较,通过调整相位或频率来使两个信号保持同步。最终,FMPLL的输出信号将具有稳定的频率和相位。

FMPLL在通信系统中具有重要作用,能够提供稳定的时钟信号,使系统能够准确地接收和发送数据。它还可以用于音频处理、信号调制和解调等应用中,以实现精确的频率调制和解调操作。

6.Crossbar switch architecture 交叉开关架构

Crossbar switch architecture for concurrent access to peripherals, flash memory, or RAM from multiple bus masters。

交叉开关架构用于实现多个总线主设备对外设、闪存存储器或随机存取存储器(RAM)的并行访问。

在多总线主设备系统中,交叉开关架构扮演着重要的角色。它允许多个总线主设备同时访问不同的外设、闪存存储器或RAM。这种架构的设计可以提高系统的并行性和效率,并支持多任务处理。

通过交叉开关架构,系统中的不同总线主设备可以通过交叉开关相互连接,形成多个通路。总线主设备可以通过这些通路并行地访问外设、闪存存储器或RAM,而不会相互干扰或造成冲突。

这种并行访问的结构可以提供更高的系统性能,增加数据吞吐量,并支持同时进行多个数据传输或多个任务的执行。交叉开关架构在高性能电子系统中被广泛应用,例如计算机系统、网络交换机和嵌入式系统等。

7.Boot assist module (BAM) 引导辅助模块

Boot assist module (BAM) supports internal flash programming via a serial link (CAN or SCI)

引导辅助模块(BAM)的电路结构可以因厂商和具体的设计而有所不同,但一般会包括以下几个主要组成部分:

-

串行链路接口:BAM通常会提供一个串行链路接口,用于与计算机或其他设备进行通信。常见的串行链路包括CAN(控制器局域网)和SCI(串行通信接口),它们可根据具体需求选择。

-

数据接收和发送模块:BAM中通常包含数据接收模块和数据发送模块,用于在串行链路上接收和发送数据。接收模块负责接收来自计算机或其他设备的引导命令和数据,而发送模块负责将编程数据传输到内部闪存。

-

数据缓冲区:BAM可能会包含一个或多个数据缓冲区,用于临时存储接收到的或将要发送的数据。数据缓冲区可以帮助平衡数据传输的速度,保证数据的完整性和正确性。

-

控制逻辑:BAM中的控制逻辑用于协调和控制整个编程过程。它可以进行接收和发送数据的时序管理,处理引导命令和数据的解码与验证,以及控制闪存编程时的信号交互。

-

闪存编程电路:BAM中还可能包含用于与内部闪存进行连接和通信的电路。这些电路可以根据具体的闪存类型和接口进行设计,以实现对内部闪存的编程操作。

需要注意的是,BAM的具体电路结构会因厂商和产品而有所不同。一些BAM可能还包含额外的功能模块,如编程时序生成器、电源管理模块等,以满足特定的系统需求和设计要求。

综上所述,引导辅助模块(BAM)的电路结构包括串行链路接口、数据接收和发送模块、数据缓冲区、控制逻辑和闪存编程电路等组成部分。这些模块协同工作,实现对内部闪存的编程支持和引导过程管理。

8.Enhanced Modular Input Output System-lite(eMIOS-lite)增强型模块化输入输出系统

eMIOS-lite(Enhanced Modular Input Output System-lite)是一种嵌入式系统中的模块化输入输出系统。它是一种用于处理各种定时和计数任务的硬件模块,通常用于嵌入式控制系统和汽车电子中。

eMIOS-lite提供了用于定时和计数的高度灵活的功能。它可以配置为具有多个输入捕获通道、输出比较通道和脉冲宽度调制(PWM)通道,以满足不同应用的需求。

输入捕获通道可用于测量外部事件的时间间隔,并将结果存储在寄存器中。输出比较通道可用于生成比较信号,用于触发特定事件或进行定时控制。而PWM通道可用于产生具有可调节占空比的脉冲信号,广泛应用于电机控制、照明控制等领域。

eMIOS-lite还具有模块化的设计,允许用户根据具体需求动态配置其功能。它提供了一种灵活的方法来实现各种定时和计数任务,提供精确的时间测量和控制能力。

需要注意的是,具体的eMIOS-lite功能和配置可能因厂商和产品而有所不同。每个厂商会根据其特定要求和目标应用来设计和实现eMIOS-lite模块,因此它在不同系统中的具体实现方式可能会有所差异。

总结来说,eMIOS-lite是一种嵌入式系统中的模块化输入输出系统,提供定时和计数功能,包括输入捕获、输出比较和脉冲宽度调制等功能。它的灵活性和可配置性使其成为广泛应用于嵌入式控制系统和汽车电子领域的重要硬件模块。

9.DSPI、SPI、QSPI

答:

SPI、DSPI和QSPI在物理层面上使用不同的接口来进行数据传输。以下是它们常用的接口类型:

-

SPI接口:SPI使用四根信号线进行通信,包括:

- SCLK(Serial Clock):时钟线,由主设备提供并控制数据传输的时序。

- MOSI(Master Output Slave Input):主设备输出,从设备输入的数据线。

- MISO(Master Input Slave Output):主设备输入,从设备输出的数据线。

- SS/CS(Slave Select/Chip Select):片选信号线,由主设备选择与之通信的从设备。

-

DSPI接口:DSPI与SPI接口类型相似,但可兼容更高频率和更多的功能。DSPI接口通常使用以下信号线:

- SCLK(Serial Clock):用于时钟传输。

- PCS(Peripheral Chip Select):外设片选信号线,用于选择与主设备进行通信的外设。

- SIN(Serial Input):串行输入线,用于数据传输。

- SOUT(Serial Output):串行输出线,用于数据传输。

-

QSPI接口:QSPI接口是在SPI基础上进行扩展的高速串行接口。它允许并行传输数据,以提高传输速率。QSPI接口通常使用以下信号线:

- SCLK(Serial Clock):用于时钟传输。

- CS(Chip Select):片选信号线,用于选择与主设备进行通信的外设。

- IO0, IO1, IO2, IO3:四根并行数据线,用于高速数据传输。

需要注意的是,具体使用的接口类型和信号线数量可能因芯片制造商和具体设计而有所不同。在选择和使用这些接口时,应仔细查阅相关芯片的规格和设计手册,确保正确配置和连接信号线。

DSPI(Digital Serial Peripheral Interface),SPI(Serial Peripheral Interface)和 QSPI(Quad Serial Peripheral Interface)都是串行外设接口协议,用于在嵌入式系统中连接和通信多个外部设备。它们之间的区别如下:

-

SPI(Serial Peripheral Interface)是最基本的串行外设接口协议。它使用主从模式,其中一个设备(主设备)控制通信的时序和数据传输,而其他设备(从设备)响应主设备的操作。SPI协议只支持单向或半双工的数据传输。

-

DSPI(Digital Serial Peripheral Interface)是SPI的一种扩展和增强版本。DSPI协议在SPI的基础上提供了更多的功能和扩展能力。与SPI相比,DSPI支持全双工通信,即可以同时进行双向的数据传输。此外,DSPI协议还支持多个从设备的连接,通过片选信号进行设备选择。

-

QSPI(Quad Serial Peripheral Interface)是SPI的高速变种。与SPI和DSPI不同,QSPI协议使用四根数据线(Quad)进行并行通信,从而提供更高的数据传输速率。QSPI通常用于需要更高带宽和更快传输速度的应用,例如存储器和图像传感器等设备。

总结来说,SPI是最基本的串行外设接口协议,DSPI是对SPI进行了扩展和增强,提供了全双工通信和多从设备连接的能力,而QSPI则是在SPI基础上提供了更高的数据传输速率。选择使用哪种协议取决于具体的应用需求和外部设备的要求。

10.periodic interrupt timers (PIT) 周期性中断定时器

Up to 6 periodic interrupt timers (PIT) with 32-bit counter resolution.

周期性中断定时器(PIT)是一种硬件模块,通常用于计时和生成周期性的中断信号。它可以用于各种应用,例如定时器、计时器、任务调度等。

PIT的主要功能是生成周期性的中断信号。它通过设置定时器的计数值和预定的时间间隔来控制中断的触发频率。当计数器达到预设的值时,PIT会产生一个中断信号,通知处理器执行预定的操作,如更新计时器、执行特定的任务等。

在实际应用中,PIT可以用于各种定时和时间截断操作。例如,它可以用于定时器功能,实现定时触发特定的事件或操作。它还可以用于实时系统中的任务调度,确保任务按照指定的时间间隔执行。此外,PIT还可以用于测量时间间隔或实现其他计时和计数的功能。

总之,周期性中断定时器(PIT)是一种用于生成周期性中断信号并进行定时和计时操作的硬件模块。它在很多应用中发挥着重要的作用,提供了精确的时间控制和任务调度功能。

11.System Module Timer (STM) 系统模块计时器

System Module Timer (STM) 是一种硬件模块,用于提供系统级的计时和调度功能。它通常用于处理器内部,与其他系统组件和模块进行时间同步和协调。

STM 的主要功能包括:

- 计时和周期性触发:STM 可以提供精确的计时功能,例如测量执行时间、时间戳记录等。它也可以生成周期性的中断信号,用于实现定时操作。

- 性能监控:STM 可以收集和记录各种系统性能指标,如处理器周期、指令执行时间、缓存命中率等。它对于系统性能优化和调试非常有用。

- 事件跟踪:STM 可以捕获和记录特定事件的发生时间和顺序,用于进行系统级的事件分析和调试。

- 外部时钟同步:STM 可以与外部时钟源进行同步,以确保系统各个部件的时间一致性。

STM 在嵌入式系统和实时系统中经常被使用,用于精确计时、性能监控和系统调度。它是一个重要的系统级组件,可以提供时间相关的功能和服务,帮助提高系统性能和稳定性。

12.Nexus development interface (NDI) Nexus开发接口

NDI 的中文翻译可以是「Nexus开发接口」或「Nexus调试接口」。

关于 NDI 使用的引脚,它通常是通过 JTAG(Joint Test Action Group)或者 SWD(Serial Wire Debug)等接口实现的。具体使用的引脚数量和分配会根据实际的芯片和开发板而有所不同。一般来说,这些引脚包括以下几个:

- TMS(Test Mode Select):用于控制 JTAG/SWD 接口的模式选择。

- TCK(Test Clock):JTAG/SWD 接口的时钟信号。

- TDI(Test Data Input):用于向目标处理器发送调试数据或命令。

- TDO(Test Data Output):用于从目标处理器接收调试数据或响应信息。

- RESETn(Reset):用于对目标处理器进行复位操作。

- VCC(Power):提供供电电源。

- GND(Ground):接地引脚。

需要注意的是,不同的芯片和开发板可能会使用不同的引脚分配和命名约定。因此,在具体的应用中,需要参考相关的芯片手册、开发板文档或调试工具的规格说明来了解具体的引脚配置和用途。

Nexus Development Interface (NDI) 是一种调试和故障排除接口,用于与嵌入式系统中的处理器进行通信。它是一种硬件接口,允许开发人员通过调试工具与处理器进行交互,以进行代码调试、性能分析和系统级调试。

NDI 提供了以下功能:

- 读取和修改寄存器的值:开发人员可以使用 NDI 读取和修改目标处理器的内部寄存器的值,以便观察和控制处理器的状态。

- 访问调试事件:NDI 可以在目标处理器上捕获和记录调试事件,例如断点、单步执行和触发异常等,以帮助开发人员分析代码的执行过程。

- 实时追踪和性能分析:通过 NDI,开发人员可以获取实时的指令执行信息、缓存命中率、函数调用时间等性能数据,以进行系统级的性能分析和调优。

- 调试接口扩展:NDI 还可以支持额外的接口扩展模块(例如Trace Port Interface Unit),以提供更丰富的调试功能,如跟踪执行流、内存访问等。

NDI 可以用于各种处理器架构和芯片厂商的嵌入式系统开发,为开发人员提供强大的调试和故障排除能力。它是嵌入式系统开发中重要的工具之一,有助于加速开发周期和提高代码质量。

13.Joint Test Action Group (JTAG) 联合测试行动组

Device/board boundary Scan testing supported with per Joint Test Action Group (JTAG) of IEEE (IEEE 1149.1)

支持每个 IEEE(IEEE 1149.1)的联合测试行动组(JTAG)进行设备/板边界扫描测试。

14.On-chip voltage regulator (VREG) 片上电压调节器

On-chip voltage regulator (VREG) for regulation of input supply for all internal levels MPC5604B/C Microcontroller Data Sheet.

MPC5604B/C 微控制器数据表中提到了用于调节所有内部电平输入供电的片上电压调节器(VREG)。

片上电压调节器(Voltage Regulator On-Chip,简称 VREG)是集成在芯片内部的电路,用于调节芯片内部电路和逻辑电平所需的供电电压。

芯片内部的各个模块和电路通常需要不同的电压来正常运行。而不同的外部供电源可能提供的电压并不总是与内部电路的工作电压相匹配。这就需要通过片上电压调节器来将外部供电源的电压进行适当的调节,以满足内部电路的工作要求。

片上电压调节器通常由电路设计师根据芯片需求和性能指标进行设计和实现。它通常包括一个反馈回路,用于稳定输出电压并对输入电压的变化做出调整。常见的片上电压调节器类型包括线性稳压器(Linear Regulator)和开关稳压器(Switching Regulator)。

通过具有片上电压调节器的芯片,可以提供稳定、可靠的供电电压给内部模块和电路。这有助于确保芯片的正常工作,提高系统性能和可靠性。

15.PWM + MC + IC/OC

在芯片手册中,PWM + MC + IC/OC 表示脉冲宽度调制(PWM)功能结合了模块控制(MC)和输入/输出比较(IC/OC)功能。

-

MC(Module Control):MC 是一种模块控制功能,可用于对 PWM 模块进行配置和控制。通过 MC,可以设置 PWM 的工作模式、时钟源、计数器周期等参数。它提供了对 PWM 模块的灵活性和可编程性,使得可以根据具体应用的需求进行配置和操作。

-

IC/OC(Input/Output Compare):IC/OC 是输入/输出比较功能,用于与 PWM 模块的计数器进行比较。在 PWM 输出信号的周期内,可以使用 IC/OC 来比较计数器的值与预设的阈值,以产生各种不同的操作和响应,例如改变输出电平、触发事件或响应外部输入等。

综合起来,PWM + MC + IC/OC 是指 PWM 模块集成了模块控制和输入/输出比较功能,通过模块控制可以对 PWM 进行配置和控制,而输入/输出比较功能可以对 PWM 的计数器进行比较和操作,以实现各种精确的脉冲宽度调制应用。

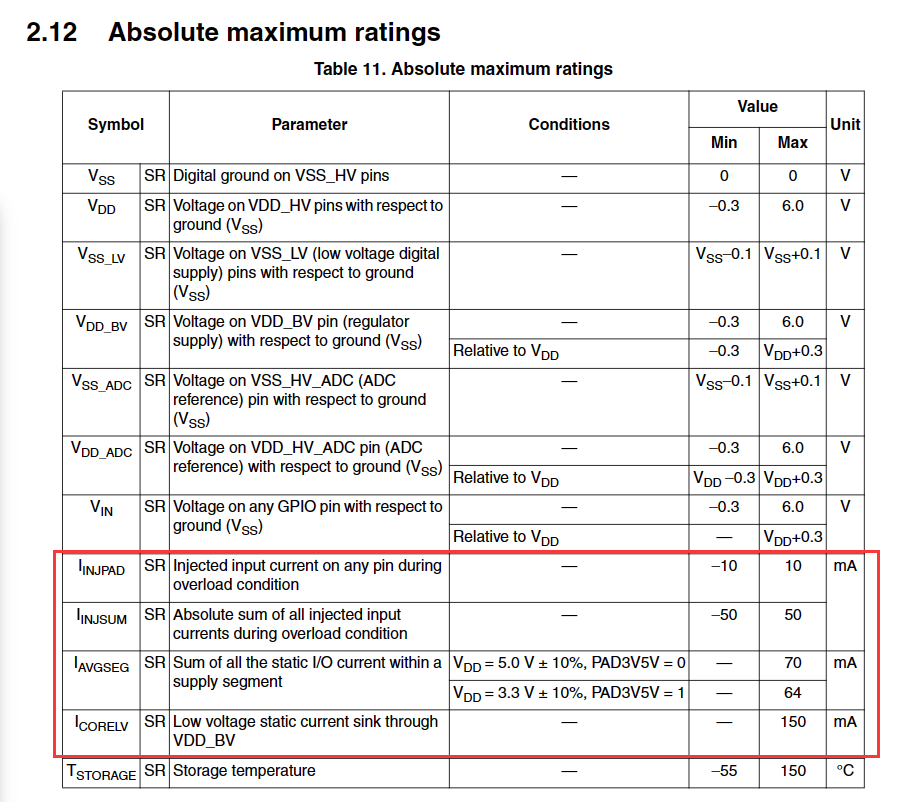

16.四个电流直标

这四个电流指标有以下区别:

-

“Injected input current on any pin during overload condition”(过载条件下任意引脚的注入输入电流):当某个引脚在过载条件下,即接收到异常高电流时,所注入的电流。这个指标描述了引脚在过载情况下可能引入的电流。

-

“Absolute sum of all injected input currents during overload condition”(过载条件下所有注入输入电流的绝对和):在过载条件下,所有引脚注入输入电流的绝对值之和。这个指标表示了在过载情况下,所有引脚注入输入电流的总和,其中包括正负极性的电流值。

-

“Sum of all the static I/O current within a supply segment”(供电段内所有静态输入/输出电流之和):在一个供电段内,所有静态输入/输出电流的总和。这个指标描述了在给定供电段内,所有静态输入/输出电流的累加值,它代表了该供电段的总静态电流消耗。

-

“Low voltage static current sink through VDD_BV”(通过VDD_BV的低压静态电流引出):通过VDD_BV引出的低压静态电流。这个指标描述了在特定引脚(VDD_BV)上,通过它引出的低电压静态电流的消耗。

总结来说,这四个电流指标分别描述了引脚在不同工作条件下的电流情况。第一个和第二个指标与引脚在过载条件下的电流注入相关,第三个指标描述了供电段内的静态电流消耗,而第四个指标涉及通过特定引脚的低电压静态电流消耗。